Vivado AXI4-stream 总线设计,Vivado仿真工程.

”Vivado仿真工程 AXI4-stream总线 FPGA VerilogHDL“ 的搜索结果

AXI4系列总线简介 AXI4-lite总线 通道信号时序要求 读写的时序图 写时序的可综合程序 读时序的可综合程序 JESD的AXI配置调试心得 AXI4系列总线简介 Advanced eXtensible Interface (AXI)是ARM的Advanced ...

Vivado 中的block design是使用RTL IP形式的图形表示进行设计,在block design中使用 RTL 模块的方便之处在于,它将自动检测某些类型的信号,例如时钟、复位和总线接口,然后,检测这些信号进行IP间的自动化连接。...

AXI-stream总线主从仿真源码+时序图.可以直接加入vivado进行仿真、测试

本文主要介绍AXI Stream总线的端口定义、数据传输流程,以及仿真测试结果。

AXI4-stream总线协议不同于AXI4-lite是AXI4-full协议。后者是基于内存映射的,传输时需要提供要操作的内存地址。而AXI4-stream是面向流的传输,不涉及到内存地址。就像串口发送数据的时候,只按一定的波特率往出发送...

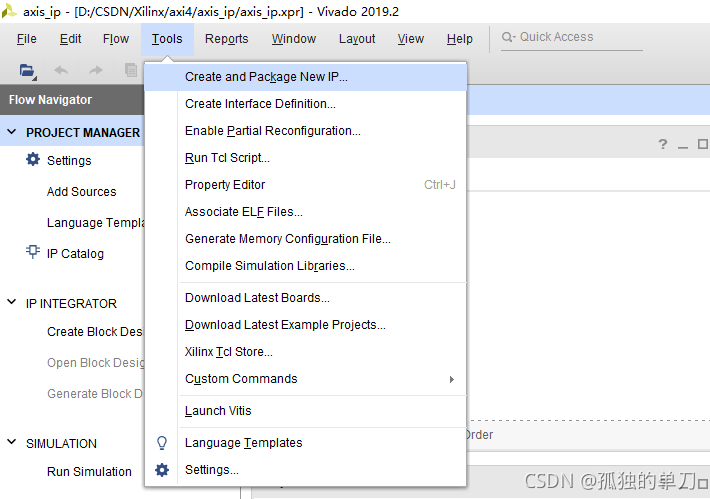

转载:原文 ...但是从机模式是被动接收数据,而不能主动的去获取数据,因此计划研究一下AXI Master接口的IP核的构建方法。 1. 利用向导创建AXI Lite Master测试用例 在这一步,AXI类型为...

基于Xlinx 的AXI4_Full手撕AXI_Full Master接口,采用Verilog实现,支持1~256的Burst_len,并对设计进行仿真验证。

vivado提供了一个AXI VIP设计实例,接下来就生成IP设计实例,并且仿真这个设计案例。

Vivado的AXI时序

标签: FPGA

AIX-stream FIFO 实现CUP与FPGA数据流交互基于地址形式的交互与基于流形式的交互AXI-stream FIFO数据读写测试AXI-stream总线读写协议AXI-FIFO与CPU数据交互PS发送数据,PL读取实验 基于地址形式的交互与基于流形式的...

仿真通过AXI_lite接口读写寄存器时axi_awready信号无法拉高的一种原因

VIVADO 官方AXI DMA模块 SG 模式 AXI DMA模块说明 AXI DMA框图 [外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-eaSKzxb8-1612687813841)(…/AXI_DAM_SG_Multichannel.assets/image-...

AXI4-lite协议介绍 AXI4-lite是AXI4-full的简化版。用于简单、低吞吐量的内存映射通信。主要用于内核和外设寄存器...再比如,在PL写一个用于PS端操作的外设时,其外设寄存器一般通过AXI4-lite总线和PS交互。 AXI4...

在Vivado中,FIFO AXI模式指的是使用AXI(Advanced eXtensible Interface)总线协议来实现FIFO(First-In-First-Out)功能的模式。根据所提供的引用内容,我们可以得出以下结论: 1. AXI Memory Mapped和AXI4-...

待补充,预计完成时间为8月4号前。本文主要为pg059的学习笔记。

背景:FPGA的系统搭建中必定出现DMA和AXI总线的相关内容。 目的:介绍DMA与AXI总线的相关知识,以便理解与应用。 相关内容: FPGA基础知识(一)UG998中FPGA相关的硬件知识与基本结构 FPGA基础知识(四)UG902 ...

平台:vivado2017.4 芯片:kintex-7 xc7k325tffg900-2 学习AXI总线。上一篇学习了AXI BRAM 和AXI_Stream FIFO。这里使用仿真看看他们之间的通信,为了更加深入的理解AXI总线。 前面分析了,AXI_BRAM的信号,支持...

推荐文章

- java中使用mysql查询 条件中含有中文时查询不到结果_Mybatis使用MySQL模糊查询时输入中文检索不到结果怎么办...-程序员宅基地

- MFC中线程间通信--主线程与子线程间的通信_mfc中主进程和子线程共享数据-程序员宅基地

- 2020年第二届“网鼎杯”网络安全大赛 白虎组 部分题目Writeup_网鼎杯网络安全大赛比赛题目-程序员宅基地

- 使用Sonatype Nexus Repository Manager上传jar包_sonatype sonatype nexus repository manager 上传jar-程序员宅基地

- 6位数密码C++破解程序,并附上时间_6位数字密码攻破-程序员宅基地

- 图解TensorFlow op:tf.nn.space_to_depth_space-to-depth-程序员宅基地

- 找不到 cl.exe 解决办法-程序员宅基地

- (Linux)kill命令常用技巧_kill -g-程序员宅基地

- 用inkscape临摹logo_inkscape 画平行四边形-程序员宅基地

- 实现哈希表的相关运算算法_建立关键字序列(16,74,60,43,54,90,46,31,29,88,77)对应的哈希表a[0-程序员宅基地